| 最優良文章 | 晶圓翹曲之應力分析技術

作者:

陳冠州、黃智勇、王慶鈞、李昌駿、劉彥禹、張詠瑄

刊登日期:2020/05/28

摘要

矽晶圓在加工的過程中,會因為各層材料之間機械性質的不匹配,而產生撓曲的現象。其中,氮化矽薄膜在半導體產業中有許多重要應用,其薄膜在製造時,受到製程溫度與壓力參數等的影響,造成晶圓翹曲的發生,將對於要求高平坦度的後續製程產生不良影響,因此,本研究欲透過模擬預測該薄膜晶圓翹曲量及內應力。根據有限元素模擬結果和實驗量測數據,氮化矽薄膜翹曲後產生的內應力,在兩者之間僅有4.2%的誤差。故藉由本研究之模擬方法,即可快速預測出實際加工之前氮化矽薄膜的本質應力、薄膜成長後的內應力與翹曲量。

During the processing of silicon wafers, the phenomenon of warpage occurs due to the mismatch of mechanical properties between layers. For silicon nitride thin film, it has many important applications in semiconductor industries. When this concerned film is deposited, it is mainly affected by processing temperature and pressure parameters, which drive the occurrence of wafer warpage and affect the required high flatness of the subsequent processes. Therefore, this study intends to estimate the wafer warpage and induced internal stress through the present simulation methodology. According to the results of finite element analysis, only a 4.2% error for the estimated internal stress of SiNx film after warping is acquired as compared with corresponding measured data. Consequently, the magnitude of intrinsic stress and warpage of SiNx film deposited on silicon wafers can be quickly predicted by the present simulation technique.

關鍵詞(Keywords)

電漿輔助化學氣相沉積、氮化矽薄膜、應力模擬

Plasma-enhanced chemical vapor deposition (PECVD); Silicon nitride film; Stress simulation

前言

氮化矽(SiNx)薄膜有優異的光學、電學與機械性能,所以被廣泛運用在半導體及其相關領域。舉例來說,氮化矽因為擁有高介電係數(Dielectric constant)與高崩潰電壓(Breakdown voltage),可以降低從閘極往基極方向的漏電流,進而減少晶片的功耗,可取代氧化矽作為介電材料[1]。除此之外,氮化矽有高折射率,因此用於多晶矽(Polysilicon)太陽能電池中做為抗反射層[2-3]。在半導體產業中,氮化矽薄膜有非常多重要的功能,例如可在表面做為鈍化保護層(Passivation layer)[1, 4-6]、控制元件的本質應力[5-6, 8]、做為氧氣與水氣的阻障層(Barrier)等等[4-5]。目前常見許多不同的方法可以製備出氮化矽薄膜,例如大氣壓化學氣相沉積,低壓化學氣相沉積,以及電漿輔助化學氣相沉積(Plasma-enhanced chemical vapor deposition, PECVD)。其中,因為有電漿輔助提供反應所需的能量,故只有PECVD技術可以在不超過攝氏400度的低溫下進行[4-7],適合用於氮化矽、氧化矽與氮氧化矽等薄膜的製程。在矽晶片上沉積氮化矽薄膜時,由於其中的殘留應力(Residual stress),薄膜經常會產生嚴重的翹曲。此處所謂之殘留應力亦可稱為內應力,可以分成兩種:外質應力(Extrinsic stress)與本質應力。外質應力是因為不同材料之間的熱膨脹係數不匹配;由於薄膜製程經常處於高溫環境,當製程結束回到室溫時,會產生非常大的應力。至於本質應力的是因為不同材料之間晶格不匹配,以及薄膜成長過程中材料相態變化的效應等[9]。如果晶圓翹曲程度過大,會造成後續製程加工諸多困難,降低元件的產率與性能。在實驗中,透過調整PECVD的輸入參數,可以改變薄膜的內應力,其中,NH3與SiH4氣體流率比值及射頻功率為影響薄膜組成的主因[10],也會影響晶圓的翹曲量。

薄膜應力估算理論及PECVD參數之影響

在薄膜應力分析相關的理論研究中,最為人所熟知的即是Stoney所提出的薄膜應力模型,其假設基板材料為均質(Homogeneous)、各向同性(Isotropic)且材料性質為線彈性(Linear elastic)、薄膜厚度hf 遠小於基板厚度hs、結構厚度遠小於結構寬度、不考慮厚度方向的應力,並忽略結構之邊界效應[11]。由翹曲之曲率率半徑ρ、基板的楊氏係數 Es 與蒲松比νs,可計算薄膜應力為:

(1)

(1)

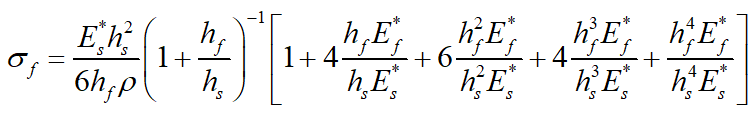

藉由基板於製程後產生之彎曲曲率,可以預測薄膜之殘留應力。但是當基板厚度並非遠大於薄膜厚度大小時,Stoney方程式不適用,故Freund等人提出可用於薄化後的基板上沉積的薄膜計算[12],其薄膜應力表示為:

(2)

(2)

其中

, (3)

, (3)

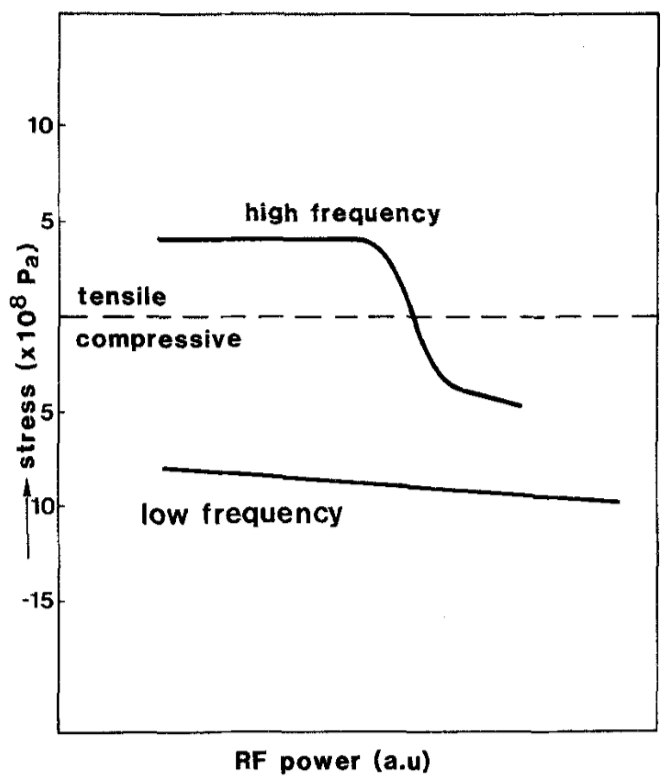

此修正公式延伸自Stoney方程式,並進一步考慮了薄膜厚度對於基板彎曲曲率之影響。Hsueh則在2001年提出了由殘餘應力與外部力矩而引起的多層薄膜變形,由通解可求得在多層薄膜中殘餘應力的分布情形[13],若簡化為單層薄膜與基板的翹曲,則其平均薄膜殘餘應力σf為:

(4)

(4)

此方程式不僅考量到薄膜厚度的影響,也考慮沿著厚度方向上不同的彎曲應力;透過其結構彎曲變形,找出曲率半徑與薄膜應力之關係式。

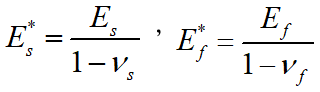

圖1 PECVD參數與SiNx薄膜應力關係圖[14]

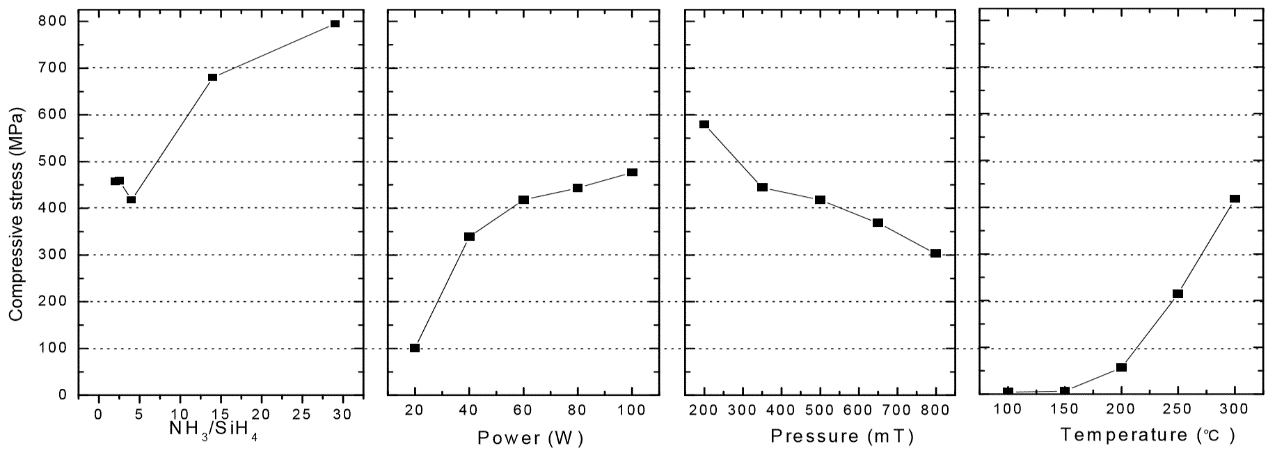

圖2 射頻功率對本質應力的影響[16]

另一方面,欲計算氮化矽薄膜經由PECVD製程沉積於晶圓表面後所受到的內應力,必須先得知氮化矽形成薄膜後具有的本質應力。在Li等人的研究中,藉由系統性地改變製程參數,例如:反應氣體流率、腔體氣壓、基板溫度與射頻功率等條件,配合其所沉積出的氮化矽薄膜,實際測量薄膜折射率、密度與紅外光譜,分析上述參數對本質應力的影響。結果如圖1所示。該圖顯示射頻功率、基板溫度,以及NH3與SiH4兩者氣體流率比值愈大,則本質應力愈大;而腔體氣壓則是與本質應力呈反比[14]。此外,Morin等人的研究中也顯示NH3與SiH4氣體流率比值愈大,意即在矽含量較低的薄膜中,其本質應力較大[15]。Claassen等人的研究,則提到在射頻頻率高於4MHz時,薄膜內應力會隨著功率增加,由拉伸應力轉變為壓縮應力;射頻頻率低於4MHz時,薄膜內應力為壓縮應力,其絕對值會隨著功率增加而上升[16],分析結果如圖2所示。

…本文未結束

更完整的內容 歡迎訂購 2020年6月號 447期

機械工業雜誌‧每期240元‧一年12期2400元

我要訂購