|本期最優良文章| 智能化晶圓熱壓合設備開發

摘要

電子4C產品的薄化、微小化快速發展,效能的多功運算及智能化的整合需求趨勢下,產品內部的控制IC晶片也必須同步升級。電子封裝技術就扮演實現IC整合的重要地位,其中封裝技術及設備的優異不僅關係到整體IC的運作效能,生產線良率的穩定性更是影響甚大。目前國外設備對此也導入智能化的監測平台及製程手法加以改善。有鑒於此,國內業者也應加緊跟上腳步。本文即針對先進封裝技術說起,接著說明晶圓級接合技術種類及方法,並著重於目前開發的熱壓接合設備平台開發流程、智能化模擬整合的導入及未來展望。

The development trends in 4C electronic products are size miniaturization, multi-function computing, and intelligence integration, which all require function upgrade in the control IC. Electronic packaging plays an important role in multiple IC integration. The packaging technology and the process equipment used not only affect overall IC performance but also affect production line stability. At present, foreign equipment performance has been improved by introducing intelligent monitoring platforms and process methods; pushing domestic makers to keep up with the pace. This article starts from advanced packaging, and then introduces various bonding technologies and methods used. We will focus on the development process of the thermal compression bonding equipment and intelligent simulation in the development process. The future prospects are presented as well.

關鍵詞:晶元接合、熱壓、模擬

Keywords:Wafer bonding, Thermal compression, Simulation

前言

隨著應用處理器及基頻晶片等高階晶片的效能與功能要求逐漸提高,晶片的 I/O 數也迅速增加,以便在各種晶片與元件之間傳輸愈來愈多電子訊號。為容納極高密度 I/O,必須縮減晶片內 I/O 間的距離。在市場追求更快速多樣化的發展包括智慧型手機、穿戴式產品、車輛、物連網的趨勢帶動下,晶片模組必須具有高傳輸效率、輕、薄、短、小、功能性佳、低耗能、低成本等要求,因此不僅晶片技術的提升,晶片封裝層級的封裝技術也是備受挑戰。

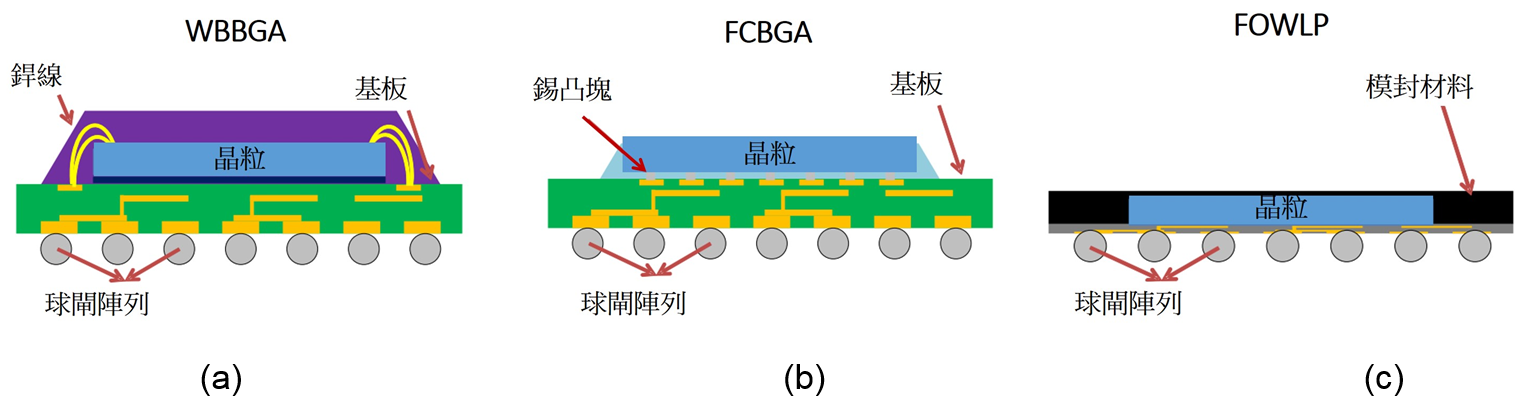

以目前封裝技術的演進,如下圖1所示,最早期晶片以陶瓷或塑膠做為基板,透過銲線連接晶片及構裝外的電路,將晶片與導線架均封裝於同一塑膠構裝內,再透過構裝外接腳連接到印刷電路板上。然而,有限的接腳數導致無法滿足較高密度I/O的需求。因此,出現以IC基板配合球閘陣列封裝(BGA)技術的方式以達到此需求。這種封裝技術將晶片放置在IC基板上,運用銲線連接基板的內建金屬線路,再利用基板下方的金屬球將基板與印刷電路板連結,如圖1(a)所示。隨著技術演進覆晶技術取代了銲線,利用錫球取代金屬接線以達到更高的I/O密度,兩者結合成為覆晶式球閘陣列封裝(FCBGA),圖1(b)所示,其電路效能與散熱效果較佳,雖然封裝技術大幅進步,但因採用IC基板,因此仍難降低成本、厚度及封裝面積,為解決成本較高及封裝尺寸較厚的問題,Infineon於2008 年推出扇出型晶圓級封裝(FOWLP),此為一「不需基板」的封裝技術,Infineon稱其為嵌入式晶圓級球閘陣列(eWLB),此技術不僅能降低成本與厚度,也達到高整合性。隨著愈來愈多一線半導體業者 ( 如台積電,該公司將 FOWLP 技術稱為InFO,即整合型扇出 )投入資源研發這項新技術,良率已大幅提升,該技術也更具成本效益。[1-5]

圖1 封裝技術演進 (a)WBBGA (b)FCBGA (c) FOWLP

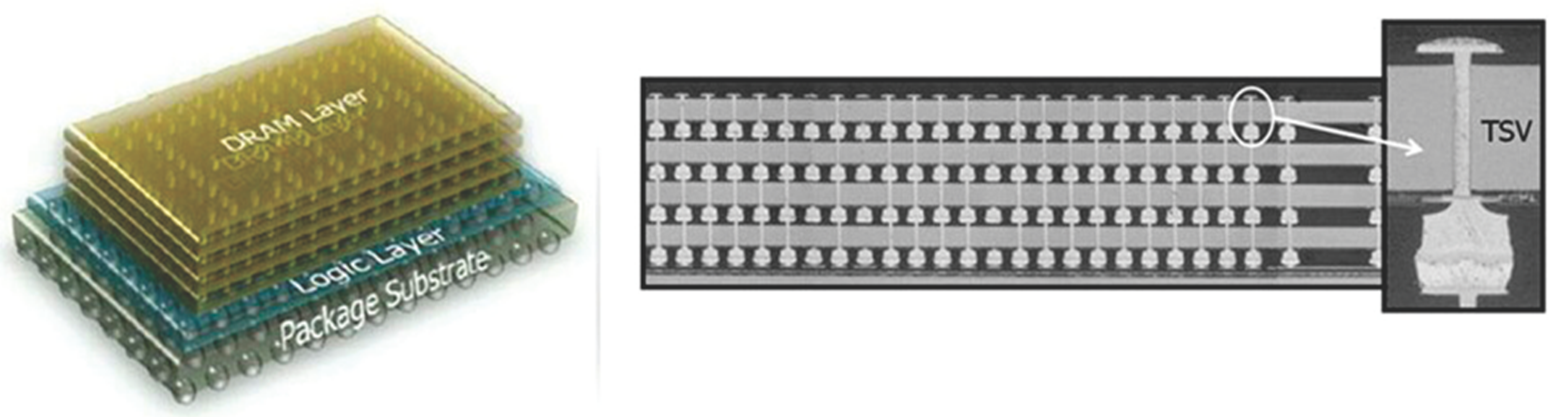

前述由小型化封裝演變成晶圓級封裝,另一方面發展,由單晶片模組變成三度空間堆疊(Stack Chip scale package, S-CSP)及多晶片封裝(Multi Chip Package, MCP)及系統封裝(System on Package, SoC),更近一步縮小體積及提高性能。其中在以3D晶圓級封裝技術,如圖2所示,透過三維堆疊方式,並利用接合技術(bonding technology),將晶片彼此接合達到堆疊效果,利用矽基板的直通孔(Through Silicon Via, TSV)做為信號連接,不僅有效縮短電流訊號距離減低功率耗損,減少電阻電容的延遲,也提供良好導熱方法,在微小化情況下達到更高效能。

圖2 Micron hybrid memory cube (HMC) [6].

由此可見在複雜封裝技術中,各項製程要求越來越高,晶圓级的封裝製程中因線路採用了半導體晶圓製程的導入,接合時的對準偏移誤差就更加嚴格,有些產品要求到0.5 μm以下的偏移誤差,另外,還有面臨異質材料、熱膨脹係數差異等種種挑戰,接著就進一步探討晶片接合技術及設備開發上可能面臨的問題。

晶圓接合技術

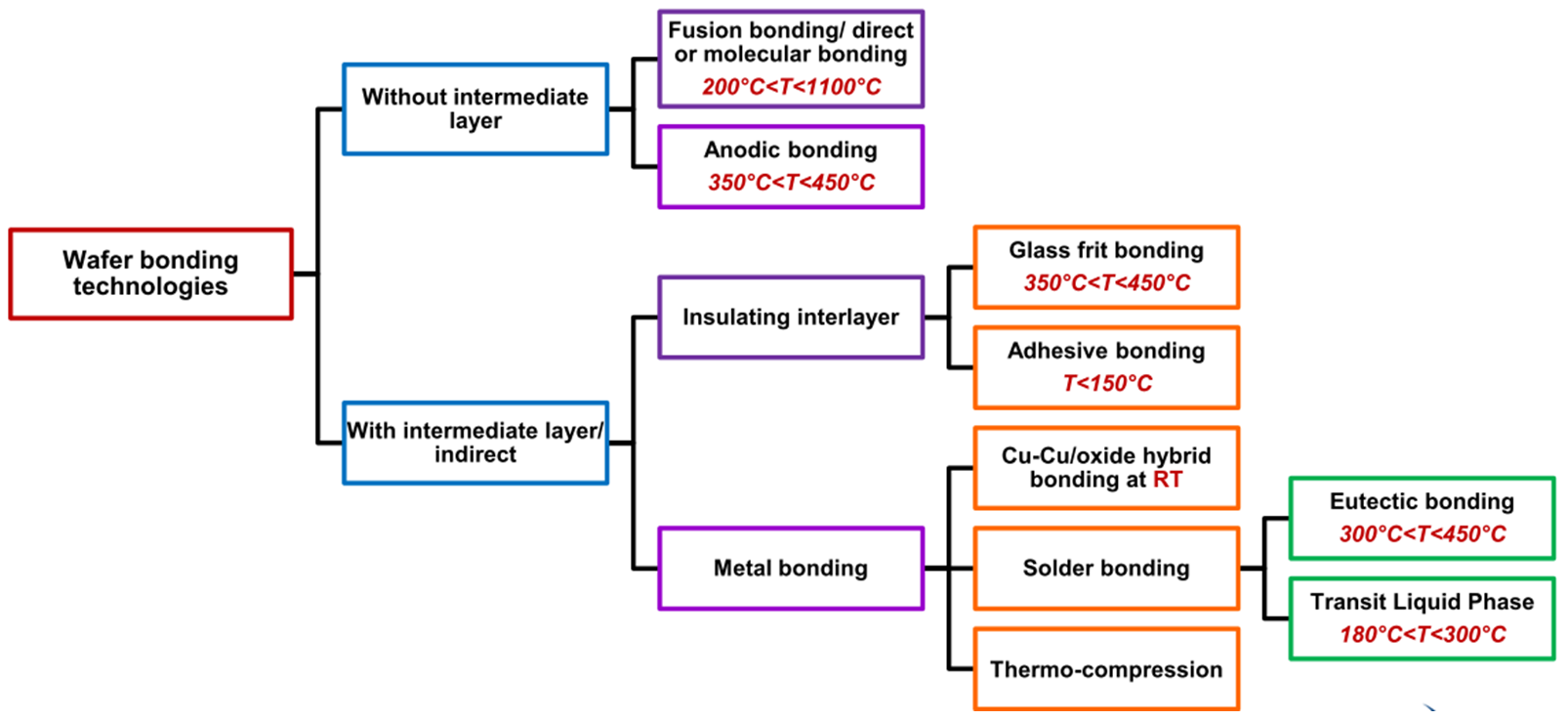

藉由Yole 2015市調報告中整理的晶圓接合技術分類,如下圖3所示,首先由接合時有無中間介質層(intermediate layer)區分為兩大類,第一類無中間介質層的製程方法包含直接接合和陽極接合兩種;第二類使用中間介質層方式,依中間介質層導電性細分,使用絕緣體材料的結合方法有玻璃膠(glass frit)及高分子材料;另外,使用導電材料的方法有銅/銅-氧化物接合、焊料接合及熱壓式接合。以下將針對上述接合方法進一步說明:

圖3晶圓接合技術分類 (Yole 2015)

1. 直接接合(direct bonding)

直接接合方法顧名思義是兩片晶圓之間無沉積任何材料,主要利用兩片晶圓間分子的化學鍵做為聯結,通常會有兩階段結合。第一階段是利用化學清潔或表面改質將晶圓表面雜質去除後進行接合,此階段在常溫下利用分子間的凡德瓦爾力(Van der Waals forces)進行貼合,第二階段會進到高溫爐進行退火 (Thermal annealing),一般來說Si/Si接合溫度約1000℃,GaAs/GaAs接合溫度約700~900℃ ,讓兩個結合面產生較高能量的共架鍵(Covalent bonds),進而達到永久接合,在正確的退火條件下其結合強度也可以等同於單一矽晶圓塊材。而此種結合方式最重要的就是晶圓表面粗糙度(microroughness)需要小於0.5nm,但利用新的表面改質方式,讓第一階段有效接合後,第二階段的退火溫度可降至400℃以下,提高此種結合方式的利用率。

…本文未結束

更完整的內容 歡迎訂購 2019年9月號 438期

機械工業雜誌‧每期240元‧一年12期2400元

我要訂購