先進封裝設備之晶圓對位技術

摘要:從台積電推出InFO (Integrated Fan Out) 的先進封裝技術開始,半導體技術論壇,以及關相關專業研討會都脫離不了先進封裝扇出型封裝 (Fan Out Package)這項議題。雖然工研院機械所目前已開發晶圓級熱壓接合設備,然此設備開發時,即定調以製程驗證無需對位功能的著眼點進行研究開發,因此,如欲以此設備進行先進封裝,製程則需整合對位技術於此設備之中。藉由本次檢索先進封裝技術之對位技術,並綜合專利地圖分析及設備專利資料,本技術論文除提供讀者對該製程技術的技術掌握度之外,藉由專利分析,更可進一步強化相關技術開發能量。

Abstract:Since the announcement of TSMC’s InFO (Integrated Fan Out) advanced packaging technology, semiconductor technology forums and professional seminars have been focused and inseparable from the topic of Fan Out Package (Fan Out Package). Although ITRI MMSL have successfully developed thermal compression bonding equipment, due to its original development standpoint focusing on process verification where alignment function is not required, the equipment is not suitable for such advanced package manufacturing process, in which process the wafer alignment function is required and plays an important role. In this article, patent analysis of the wafer alignment technology for the advanced packaging equipment is discussed with the goal to offer readers more understanding of the technology for the advanced package process equipment development.

關鍵詞:晶圓對位、先進封裝、專利分析

Keywords:Wafer alignment, Advanced packaging, Patent analysis

前言

隨著製程的進步,晶圓內的電晶體逐漸縮小至物理極限,而先進封裝被視為延伸摩爾定律的利器。由台灣-台積電推出的扇出型封裝技術,透過晶片堆疊能使晶片有更高的性能及更小的尺寸,可以滿足消費電子產品不斷增長的需求。先進封裝技術演進趨勢中,扇出晶圓級封裝(fan-out wafer-level packaging, FOWLP)技術被認為是2.5D封裝的替代方法。與扇入晶圓級芯片級封裝(fan-in wafer-level chip-scale package, WLCSP)技術相比,因為直接與IC相結合而不是打線接合或以倒晶封裝,具備無基板封裝、低熱阻以及高性能等優點,能夠實現超薄,高密度封裝的封裝製程[1]。由於市場對於輕薄短小行動裝置的需求不斷增加,因此扇出型晶圓級封裝成為行業趨勢。

隨著先進封裝發展到降低成本與提高整體性能,目前較顯著成長的應用領域包括消費電子、高效能運算與物聯網。此外,隨著半導體IC在汽車領域的日益普及,尤其是電動車與自駕車的技術愈趨成熟,近年來對先進封裝的需求也已大大增加。

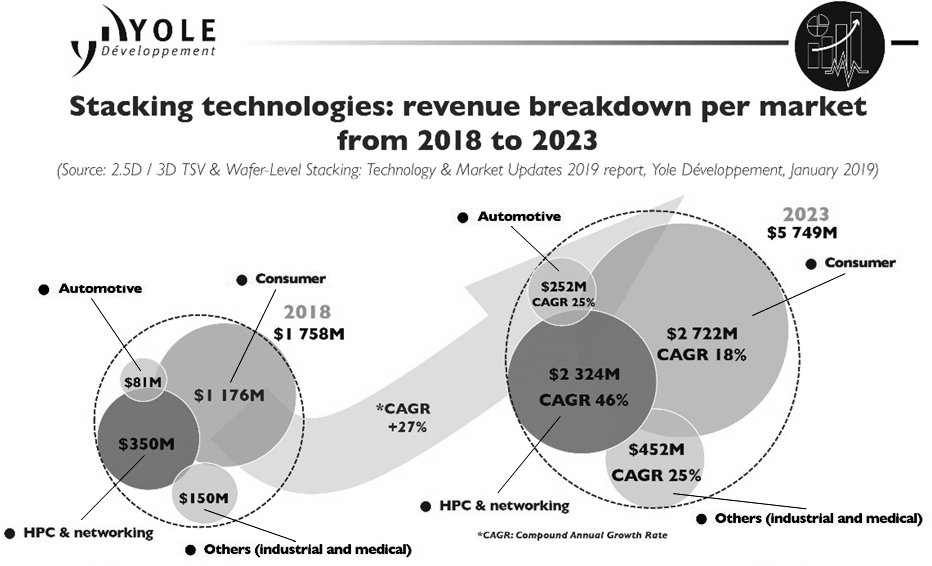

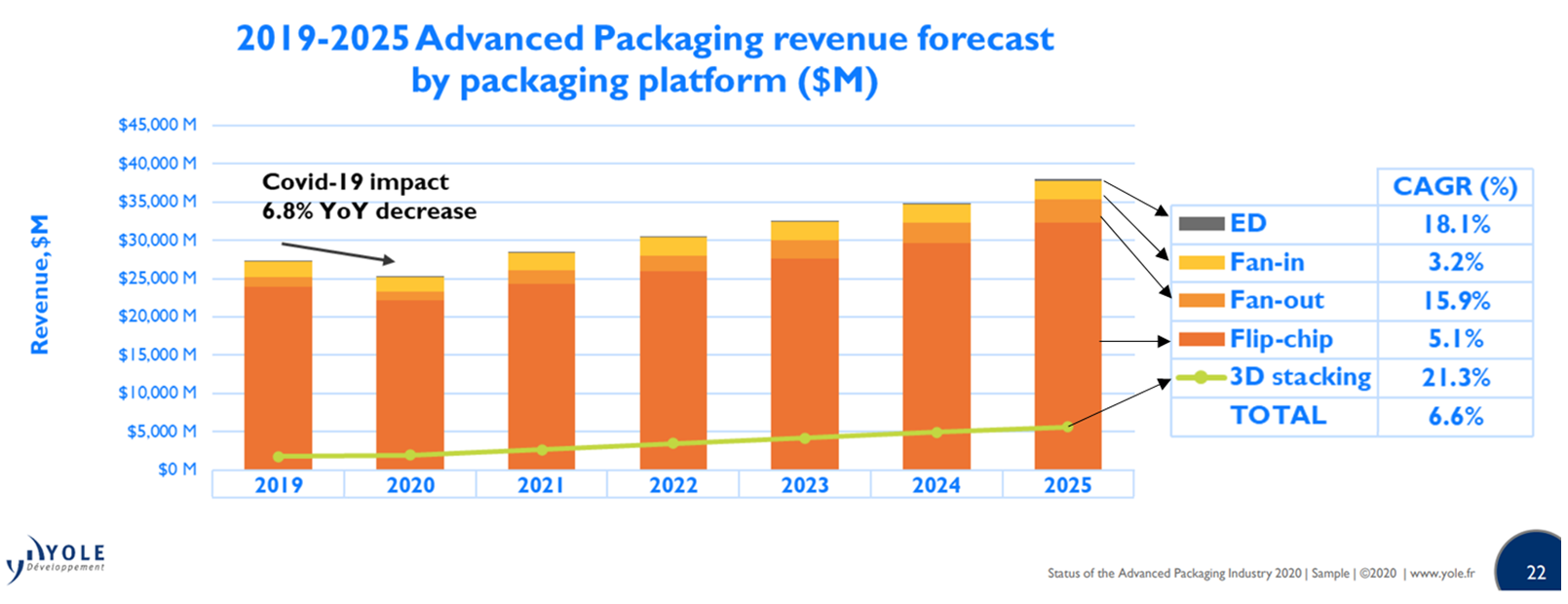

以Yole市場分析資料如圖1,2019年先進封裝市場產值超過250億美元,但隨著COVID-19的爆發,中國和日本等國家在全球市場上嚴格執行貨物運輸限制,使關鍵原材料缺料造成斷鏈,加上城市封鎖導致的勞動力問題,許多封裝和測試工廠已經減少甚至停止運營,2020年先進封裝市場產值呈現下降的趨勢。但如圖2預估在2021年開始至2025年期間,受電動車、自駕車、5G及HPC等需求,先進封裝產值呈現持續成長趨勢,複合年均增率預估將達27%。

圖1 相關應用領域產值預估 [3]

圖2 先進封裝市場現況分析 [3]

以目前的發展來看,在未來數年內,3D堆疊式DRAM及3D邏輯系統單晶片(SOC)的應用將會是3D IC最大的成長動力;接下來就是以2.5D技術切入的CMOS影像感測器、電源設備及MEMS。可預見的是3D IC的技術掀起長達十數年的晶片革命,最終3D IC的封裝技術將會成為未來半導體產業的典範。

由此複雜之先進封裝製程中,晶圓级接合時的對準技術就需更加精準。利用本次專利地圖分析,針對先進封裝設備之晶圓對位軟硬體技術分析,進一步提供國內設備廠或晶圓大廠,提升國內製程品質或開發新型製程技術。此外,工研院機械所預期開發晶圓級封裝設備,晶片封裝設備商EVG的成熟技術既是開發中的學習對象,也是開發完成後的潛在競爭對手,因此也為分析的重點之一。

…本文未結束

更完整的內容 歡迎訂購 2021年6月號 459期

機械工業雜誌‧每期240元‧一年12期2400元

我要訂購